# High Performance Field-Effect Transistor Based on Multilayer Tungsten Disulfide

Xue Liu,<sup>†,⊥</sup> Jin Hu,<sup>†,⊥</sup> Chunlei Yue,<sup>†</sup> Nicholas Della Fera,<sup>†</sup> Yun Ling,<sup>‡,§</sup> Zhiqiang Mao,<sup>†</sup> and Jiang Wei<sup>\*,†</sup>

<sup>†</sup>Department of Physics and Engineering Physics, Tulane University, New Orleans, Louisiana 70118, United States, <sup>‡</sup>School of Materials Science and Engineering, Jiangsu University, Zhenjiang, Jiangsu 212013, China, and <sup>§</sup>College of Electronic and Information Engineering, Suzhou University of Science and Technology, Suzhou, Jiangsu 215011, China. <sup>⊥</sup>These authors contribute equally to this work.

**ABSTRACT** Semiconducting two-dimensional transition metal chalcogenide crystals have been regarded as the promising candidate for the future generation of transistor in modern electronics. However, how to fabricate those crystals into practical devices with acceptable performance still remains as a challenge. Employing tungsten disulfide multilayer thin crystals, we demonstrate that using gold as the only contact metal and choosing appropriate thickness of the crystal, high performance transistor with on/off

ratio of  $10^8$  and mobility up to 234 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature can be realized in a simple device structure. Furthermore, low temperature study revealed that the high performance of our device is caused by the minimized Schottky barrier at the contact and the existence of a shallow impurity level around 80 meV right below the conduction band edge. From the analysis on temperature dependence of field-effect mobility, we conclude that strongly suppressed phonon scattering and relatively low charge impurity density are the key factors leading to the high mobility of our tungsten disulfide devices.

KEYWORDS: transition metal chalcogenide · two-dimensional · field-effect transistor · tungsten disulfide · WS<sub>2</sub>

emiconducting transition-metal dichalcogenide (TMD) MX<sub>2</sub> with the thickness of atomic level, where M represents transition metal (Mo, W) and X represents chalcogen (Se, S), has attracted a lot of attention recently due to the new emerging electrical and optical properties and its great potential in practical applications. Its atomically thin structure can be easily obtained via techniques such as the micromechanical cleavage<sup>1,2</sup> and liquid-phase exfoliation,<sup>3-5</sup> because of the weak van der Waals bonding between neighboring chalcogen/metal/chalcogen lavers. Not only bulk semiconducting TMD has the ideal size of band gap (1.1-2 eV) for the making of transistor,<sup>6</sup> but also the band gap transforms from indirect to direct when the thickness of crystal approaches single atomic layer.<sup>7–11</sup> Consequently, significant enhancement of photoluminescence<sup>8,9</sup> has been observed in monolayer MoS<sub>2</sub>.<sup>7</sup> Ultrasensitive photodetectors<sup>12</sup> based on MoS<sub>2</sub> has also been demonstrated. Moreover, the intrinsically broken valley degeneracy in

monolayers makes TMD the perfect model system for studying "valleytronics".<sup>13–15</sup> Besides the exciting optical properties, the semiconducting TMDs show excellent electrical switching properties and, therefore, is expected to hold promise in modern nanoelectronics applications. The electron mobility based on single atomic layer MoS<sub>2</sub> fieldeffect transistors (FET) ranges from  $\sim 1^2$  to  ${\sim}200~\text{cm}^2\,\text{V}^{-1}\,\text{s}^{-1}.^{16}\,\text{MoS}_2\,\text{FET}$  with  $10^8$  on/ off ratio has been achieved by using high- $\kappa$ oxide materials<sup>16,17</sup> as the top gate dielectric grown by using atomic layer deposition (ALD). However, the challenges of obtaining monolayer, complicated device fabrication process and chemically modified interface make it difficult to study the intrinsic properties. Besides MoS<sub>2</sub>, researchers are also interested in other members of this semiconducting TMD group such as WSe<sub>2</sub><sup>18-20</sup> and MoSe<sub>2</sub>,<sup>21,22</sup> which exhibit good switching behavior as well. Compared with MoS<sub>2</sub>, WSe<sub>2</sub>, and MoSe<sub>2</sub>, tungsten disulfide (WS<sub>2</sub>) has a larger band gap in both bulk crystal ( $\sim$ 1.3 eV) and monolayer ( $\sim$ 2.1 eV).

\* Address correspondence to jwei1@tulane.edu.

Received for review July 8, 2014 and accepted September 29, 2014.

Published online September 29, 2014 10.1021/nn505253p

© 2014 American Chemical Society

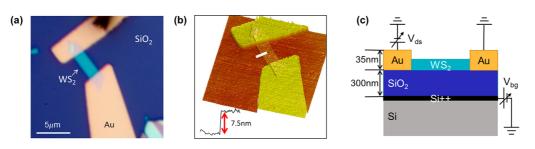

Figure 1. Device fabrication of  $WS_2$  FET. (a) Optical image of a multilayer  $WS_2$  device with gold as the contact metal and Si/SiO<sub>2</sub> as the substrate. (b) Atomic force microscope image of the device shown in (a). The inset shows the line trace of 7.5 nm thick  $WS_2$  crystal obtained at the location of white line. (c) Schematic drawing of the measurement setup for electrical transport characterization.

Although WS<sub>2</sub> is expected to have the best transistor performance (the highest on-state current density and mobility) among all semiconducting TMDs according to earlier theoretical calculation,<sup>23</sup> only a few FET studies<sup>24,25</sup> on WS<sub>2</sub> atomic crystal have been reported with the reached on/off ratio of 10<sup>5</sup> and electron mobility of 20 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, and yet, a device with performance comparable to that of MoS<sub>2</sub> has not been realized. In this paper, we report our studies on multilayer WS<sub>2</sub> field-effect transistor with simple back-gate device structure. Our devices exhibit exceptionally high on/off ratio reaching 10<sup>8</sup> and mobility up to 234  $\text{cm}^2$  V<sup>-1</sup> s<sup>-1</sup>. We have further performed low temperature measurements and revealed that minimized Schottky barrier at the contacts and appropriate impurity level plays critical roles in our WS<sub>2</sub> device.

# **RESULTS AND DISCUSSION**

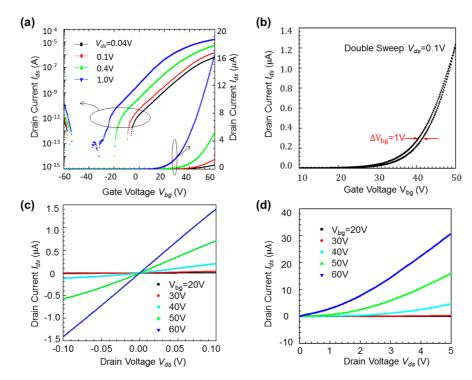

The example of as fabricated device is shows in Figure 1a,b. In this report, devices with various WS<sub>2</sub> crystal thicknesses ranging from 3 to 100 nm were studied. To characterize the electrical properties of the device, we use conventional three-terminal configuration setup with heavily doped silicon as the back-gate electrode, as illustrated by the schematic drawing in Figure 1c. On the basis of our test on more than 100 devices, we find that WS<sub>2</sub> crystals with thickness around 6-10 nm exhibit the best switching behavior (see Supporting Information for more details). Similar thickness dependence in MoS<sub>2</sub> has also been reported by Li et al.<sup>26</sup> A typical measurement of source-drain current  $I_{ds}$  vs back gate voltage  $V_{bg}$  at room temperature is shown in Figure 2a. The device appears to be n-type FET with the neutrality point of -45 V. As shown in the log scale plot of  $I_{ds} - V_{ba}$ , the device can be tuned into an off-state with the minimum current I<sub>ds</sub> less than  $10^{-14}$  A when  $V_{bg}$  is set in the range of -30 to -50 V. Also, the device has a weak ambipolar FET behavior with the sign of p-type carriers appearing at negative gate voltage ( $V_{bg} < -50$  V). The current  $I_{ds}$  at on-state can reach 20  $\mu A$  at  $V_{

m bg} \sim$  60 V with source-drain bias  $V_{\rm ds}$  = 1 V. The on/off ratio at room temperature for this device reaches 10<sup>8</sup>, which is extremely high compared with the earlier results<sup>17,19,24,25</sup> from other

semiconducting members of the MX<sub>2</sub>.<sup>16,18,24,25</sup> This is a surprising result given that we only use the device structure of back gating with 300 nm SiO<sub>2</sub> as the dielectric layer. According to the gate sweep, we can extract the gate voltage induced carrier density  $n_{2D}$  using the parallel-plate capacitor model  $n_{2D}$  =  $C_{\rm ox}(V_{\rm bg} - V_{\rm bg,th})/e$ , where  $C_{\rm ox}$  is the dielectric capacitance per unit area, V<sub>bg,th</sub> is the threshold voltage, and e is the unit charge.  $C_{ox}$  can be further calculated from  $C_{\rm ox} = \varepsilon_0 \varepsilon_{\rm r} / d_{\rm ox}$ , where  $\varepsilon_0$  is the dielectric constant of vacuum, and  $\varepsilon_r$  represents the relative dielectric constant of 3.9 for SiO<sub>2</sub>. The carrier density is estimated to be 2.6  $\times$  10<sup>12</sup> cm<sup>-2</sup> when  $V_{bg}$  = 60 V and  $V_{ds}$  = 1 V. Figure 2b shows the trace and retrace sweeps of  $I_{ds} - V_{bg}$  with  $V_{ds}$  fixed at 0.1 V. The maximum voltage difference between trace and retrace sweeps is less than 1 V indicating a small hysteresis in our device. This observation is in contrast to the relatively large hysteresis reported in other multilayer transition metal chalcogenides devices. Multiple factors, such as water or oxygen molecules absorbed on the surface<sup>27-29</sup> or charge injection at the oxide dielectric interface,<sup>30</sup> should be considered as the possible causes. Figure 2c shows the  $I_{ds} - V_{ds}$  characteristics at room temperature for different  $V_{bq}$ . At low source-drain bias from -0.1 to 0.1 V, the  $I_{ds} - V_{ds}$  presents near-linear and symmetric behavior indicating good contacts formed between gold contact metal and WS<sub>2</sub> crystal. However, when source-drain bias is swept up to 5 V, as shown in Figure 2d, the  $I_{ds}$  starts to display an upturn at  $V_{ds} = 1 \text{ V}$ , and no signs of current saturation appears even when  $V_{\rm ds}$  is increased to 5 V. To extract the room temperature field-effect mobility  $\mu$  of our device, we utilize the fieldeffect transistor model  $\mu = [dI_{ds}/dV_{ba}] \times [L/(WC_{ox}V_{ds})]$ , where L and W are the channel length and width, respectively. At room temperature, the extracted mobility of this particular devices corresponding to Figure 2 reaches 234 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at  $V_{bg} - V_{th} = 25$  V (here  $V_{\rm th}$  is the threshold voltage), which is significantly higher than the mobility (typical value of 10–180 cm<sup>2</sup>V  $^{-1}$  s<sup>-1</sup>) of MoS<sub>2</sub> devices with SiO<sub>2</sub> as the gate dielectrics.<sup>2,16,17,26,31</sup>

To reveal the origin of the high performance of our device, we have conducted low temperature transport

10397

Figure 2. Electrical property characterization of WS<sub>2</sub> device (shown in Figure 1) at room temperature. The lateral dimension is 4.8  $\mu$ m in length and 1.8  $\mu$ m in width. (a)  $I_{ds}-V_{bg}$  sweeps under different source drain voltages  $V_{ds} = 0.04$ , 0.1, 0.4, and 1 V plotted in log scale (left vertical axis) and linear scale (right vertical axis). Note: for this particular device, the maximum  $I_{ds}$  on/off ratio reaches 10<sup>8</sup> at  $V_{ds} = 1$  V and the mobility extracted reaches 234 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature. (b) Trace and retrace  $I_{ds}-V_{bg}$  sweeps at  $V_{ds} = 0.1$  V showing small hysteresis at room temperature. (c)  $I_{ds}-V_{ds}$  sweeps in small source-drain bias regime (-0.1-0.1 V) at room temperature, showing near-linear behavior. (d)  $I_{ds}-V_{ds}$  sweeps in large source-drain bias regime (0 to 5 V), exhibiting clear nonlinearity.

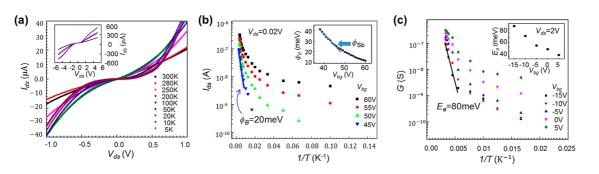

measurement and studied the detailed transport mechanism on multiple devices. A device with channel dimensions of 8 nm in thickness, 6  $\mu$ m in length and 3  $\mu$ m in width is selected for the following discussion. As shown in Figure 3a, the  $I_{ds} - V_{ds}$  sweeps are recorded with back gate voltage fixed at  $V_{bq} = 60$  V at different temperatures. It is apparent that the nonlinearity of  $I_{ds} - V_{ds}$  is enhanced when the device has been cooled from 300 to 5 K. In particular, unlike the relatively linear behavior of  $I_{ds} - V_{ds}$  sweep at room temperature, the low temperature  $I_{ds} - V_{ds}$  sweeps (T = 200-5 K) exhibit a distinct new feature: the device shows a relatively insulating state in the low source-drain bias regime  $(-0.6 \text{ V} < V_{ds} < 0.6 \text{ V})$  and a conducting state at large bias regime ( $V_{ds} > 0.6$  V or  $V_{ds} < -0.6$  V). The crossover source-drain voltage between the two regimes is around 0.6 V. Above the crossover, I<sub>ds</sub> increases rapidly with  $V_{ds}$  as can be seen more clearly in the inset of Figure 3a. We conjecture that the different temperature dependence behavior at small and large sourcedrain bias regimes may be caused by the existence of Schottky barrier, a typical situation for contacts between metal and semiconducting TMDs,<sup>32</sup> yet rarely explored in WS<sub>2</sub> device. Therefore, to highlight the possible Schottky barrier effect, we focus on the temperature dependence of source drain current at large  $V_{\rm bg}$  (60–35 V) with small  $V_{\rm ds}$  (0.02 V), as shown in Figure 3b. With large  $V_{bg}$ , the WS<sub>2</sub> crystal is tuned into

LIU ET AL.

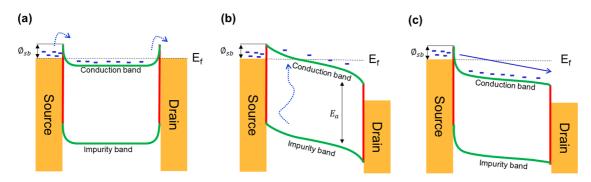

the conducting on-state as illustrated by the band diagram of Figure 4a. Thus, the total conductance of the device will be limited only by the Schottky contacts. In Figure 3b, the I<sub>ds</sub> shows a near-exponential temperature dependence from room temperature to 90 K, indicating a thermally activated charge transport mechanism. To accurately extract the Schottky barrier height of our device, we used the two-dimensional (2D) thermionic emission transport equation  $I_{ds}$  =  $\{[A^*wT^{3/2} \exp(-q\phi_B/k_BT)][\exp(qV_{ds}/k_BT) - 1]\}$  to fit our data, where A\* is the 2D Richardson constant, w is the physical width of FET, q is the unit charge,  $\phi_{\rm B}$  is the effective Schottky barrier height and  $k_{\rm B}$  is the Boltzmann constant.<sup>33</sup> By using the flat band voltage condition of  $V_{bg} = V_{FB}$ ,<sup>32,34</sup> the actual Schottky barrier height  $\phi_{\rm Sb}$  can be extracted to be 27.2 meV for this particular device as shown in the inset in Figure 3b (see more extraction examples in Supporting Information). This barrier height is comparable to the thermal energy  $(k_{\rm B}T\sim 26~{\rm meV})$  at room temperature. Therefore, the electrons at the Fermi level can be easily excited thermally to overcome Schottky barrier formed in our  $WS_2$  device, which explains the near-linear  $I_{ds}-V_{ds}$ curve at room temperature.

Intrinsic WS<sub>2</sub> crystal has an indirect band gap of 1.35 eV,<sup>11,35</sup> which in general leads to a poor gatability using thick dielectric layer of 300 nm SiO<sub>2</sub>. However, the high on–off ratio in our multilayer WS<sub>2</sub> crystal

VOL. 8 • NO. 10 • 10396-10402 • 2014

JAI

www.acsnano.org

Figure 3. Low temperature characterization. (a)  $I_{ds}-V_{ds}$  sweeps in the range of  $V_{ds} = \pm 1$  V at on-state ( $V_{bg} = 60$  V) under different temperatures from 300 K to 5K. Insert: zoomed out  $I_{ds}-V_{ds}$  sweeps in the range of  $V_{ds} = \pm 5$  V. (b) Source drain current  $I_{ds}$  (in log scale) vs temperature T (in reciprocal scale) for the same device in (a) with  $V_{ds} = 0.02$  V and  $V_{bg} = 45-60$  V. Inset: the extracted effective Schottky barrier height  $\phi_{B}$  and the arrow indicates the actual Schottky barrier height  $\phi_{Sb}$ . (c) Conductance G (in log scale) vs temperature T (in reciprocal scale) for the same device in (a) with  $V_{ds} = 2$  V and  $V_{bg} = -15$  to 5 V. Inset: the extracted thermal activation energy  $E_{a}$ .

Figure 4. (a) Band diagram of a  $WS_2$  device operating at low temperature and low source-drain bias, when the  $WS_2$  crystal is set to on-state with appropriate gate voltage. This diagram illustrates that at low temperature, Schottky barrier becomes the major factor to limit the source-drain current. (b) Band diagram of a  $WS_2$  device operating at low temperature and large source-drain bias, when the  $WS_2$  crystal is set to off-state with appropriate gate voltage. This diagram illustrates that at low temperature and large source-drain bias, when the  $WS_2$  crystal is set to off-state with appropriate gate voltage. This diagram illustrates that at low temperature thermal excitation between impurity band and conduction band is the main mechanism generating charge carriers. (c) Band diagram of a  $WS_2$  device operating at room temperature with large source-drain bias, while the  $WS_2$  is set to on-state with appropriate gate voltage. (Note: all the band diagrams are only for the purpose of illustrations and not drawn to scale.)

indicates the opposite. This unusual behavior may suggest that our multilayer WS<sub>2</sub> crystal is fundamentally different to intrinsic WS<sub>2</sub>. For conventional semiconductor, doping is the most common method to enhance the gatability of device<sup>36,37</sup> by modulating the Fermi level within the band gap. Hence, we suspect our multilayer WS<sub>2</sub> crystal may also contain impurity. To set this impurity effect apart from the Schottky barrier effect, we measured the temperature dependence of conductance at a large source drain bias  $V_{ds} = 2$  V with back gate voltage varied from -15 to 0 V as shown in Figure 3c. The purpose of applying large source drain voltage up to 2 V is to supply enough forward bias to lower the height of Schottky barrier at the drain side (illustrated by the band diagram in Figure 4b). Consequently, this favors the electron's transport toward drain electrode and minimizes the contact resistance caused by Schottky barrier. However, it is noteworthy that, because the WS<sub>2</sub> crystal is also tuned into the offstate by setting gate in the range of -15 to 0 V, the charge carriers, i.e., electrons in this case, are mostly created through thermal excitations and we assume this is the major effective mechanism that led to the

conductance of our device in this configuration. Of course, if both gate voltage and source drain voltage are set to the configuration that WS<sub>2</sub> crystal is in onstate and Schottky barriers are minimized at the contacts, the device will be turned into a highly conductive state. This situation can be easily seen in the band diagram of Figure 4c. Now, we focus on the configuration that enables us to study the thermal activation behavior, *i.e.*, large source drain bias and  $V_{bg} = -15$  to 0 V. Figure 3c shows the temperature dependence of conductance, which indeed changes exponentially from 300 to 100 K. We can fit the conductance data G with the thermal activation equation of  $G = G_0 e^{-E_a/k_BT}$ that describes the temperature dependence of conductance for thermally activated charge carriers. Here  $G_{\rm o}$  is the conductance limit at high temperature and  $E_{\rm a}$  is the thermal activation energy. As shown in the inset of Figure 3c, the extracted thermal activation energy  $E_{\rm a}$  ranges from 80 to 35 meV, which is consistent with the value also been reported in MoS<sub>2</sub>.<sup>16</sup> The obtained activation energy implies that the energy level generated by impurities is near the bottom of conduction band for our multilayer WS<sub>2</sub> crystal. Yet, the

VOL. 8 • NO. 10 • 10396-10402 • 2014

JAI

www.acsnano.org

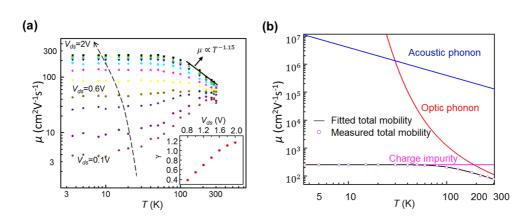

Figure 5. (a) Temperature dependence of field-effect mobility for a WS<sub>2</sub> device at different source-drain bias (0.1-2 V) with fixed effective gate voltage ( $V_{bq}-V_{th} = 25$  V). Inset: the power law constant  $\gamma$  vs source-drain bias (extracted from (a)). Dimension of the device: thickness 7.5 nm, channel length 6  $\mu$ m and channel width 3  $\mu$ m. (b) Temperature dependence of measured electron mobility (hollow circular dots) at  $V_{ds} = 2$  V and the fitted electron mobility (black line). The fitted data includes the scattering contribution from acoustic phonons (blue line), optical phonons (red line), and charge impurities (magenta line).

origin of impurity level is still under investigation and is one of the focuses in future work.

To further understand how the transport of charge carriers affected by the impurities or other possible scattering sources, we studied the temperature dependence of field effect mobility  $\mu$ . Figure 5a shows the onstate mobility at  $V_{\rm g} - V_{\rm th} = 25$  V plotted as a function of temperature at different source-drain bias ( $V_{ds} = 0.1 -$ 2 V). At small source-drain bias below 0.6 V, mobility is underestimated due to the apparent Schottky barrier. At large source-drain bias ( $V_{\rm ds} \rightarrow$  2 V), contact resistance becomes negligible, which leads to more accurate extraction of mobility. On cooling from room temperature, the mobility follows a power law ( $\mu \sim T^{-\gamma}$ ), and then remains at a saturated value below 100 K. The extracted power law constant  $\gamma$  converges toward 1.15 at  $V_{ds} = 2$  V as shown in the inset of Figure 5a.

Now we focus on the detailed charge scattering mechanism of our device, which plays a critical role in the FET performance of our devices. Similar to other TMD systems such as MoS<sub>2</sub>,<sup>38</sup> it is reasonable to consider that charge carriers in multilayer WS<sub>2</sub> crystal are usually scattered by acoustic phonon, optical phonon and charged impurities. For optical phonon scattering,<sup>16,39</sup> the temperature dependence can be described with the equation  $\mu_{op} = (4\pi\epsilon_0\epsilon_p\hbar^2/e\omega m^{*2}Z_0)$ - $[e^{\hbar\omega/k_{\rm B}T}-1]$ , where  $1/\varepsilon_{\rm p}=1/\varepsilon_{\infty}-1/\varepsilon_{\rm s}$  where  $\varepsilon_{\infty}$  and  $\varepsilon_{\rm s}$ are the high frequency and static dielectric constant, respectively.  $m^*$  is the effective mass of electron,  $\hbar\omega$  is the optical phonon energy and  $Z_0$  is the crystal thickness. For acoustic phonon scattering, under the deformation potential approximation, the mobility limited by acoustic phonons can be described by  $\mu_{ac}$  =  $e\hbar^{3}\rho\nu/(m^{*})^{2}\Xi_{\lambda}^{2}k_{B}T$ , where  $\rho$  is the crystal density,  $\Xi_{\lambda}$ is the deformation potential and  $\nu$  is the acoustic phonon velocity.<sup>38,40</sup> We shall include the background charge impurity scattering, which contributes to the mobility in the form<sup>41</sup>  $\mu_{imp} = (8\pi\hbar^3 \varepsilon^2 k_F^2 \int_0^{\pi} [\sin^2 \theta / \theta]$  $(\sin \theta + \beta)^2 d\theta / e^3 m^{*2} N_{imp})$ . Here  $\beta = S_0 / 2k_F$  and  $k_F$

LIU ET AL.

is the wavevector on the Fermi surface,  $N_{imp}$  is the impurity density and S<sub>0</sub> is the screening constant which takes the form of  $S_0 = (e^2 m^* / 2\pi \epsilon \hbar^2)$ .<sup>42</sup> Then the total mobility of a device was calculated using Mathiessen's rule  $\mu^{-1} = \mu_{op}^{-1} + \mu_{ac}^{-1} + \mu_{imp}^{-1}$  by combining contributions from all three scattering sources. Using this model, we can fit the measured mobility (circles in Figure 5b) by changing variables of optical phonon energy  $\hbar\omega$ , deformation potential  $\Xi_{\lambda}$  and charge impurity density N<sub>imp</sub> (other parameters were directly adopted from literatures of bulk WS<sub>2</sub><sup>43,44</sup>). Figure 5b shows the fitted result (black curve), which agrees well with the data from our measurement. We extracted the optical phonon energy about  $\omega \sim 240 \text{ cm}^{-1}$ , which is close to the theoretical value<sup>43</sup> of 300 cm<sup>-1</sup>. The extracted deformation potential  $\Xi_{\lambda}$  is around 2.0 eV which is also close to the value of MoS<sub>2</sub>.<sup>38</sup> The extracted charged impurity density of our WS<sub>2</sub> crystal is around  $2 \times 10^9$  cm<sup>-2</sup>, which is relatively small compared with other 2D crystals (MoS<sub>2</sub> with 1.8  $\times$  10<sup>10</sup> cm<sup>-2</sup> and grapheme with  $\sim 10^{11}$  cm<sup>-2</sup>).<sup>38,45</sup> From the fitted plot we conclude the following: (1) Charge impurity dominates the mobility at low temperature below 100 K. (2) The acoustic phonon contribution to the mobility (blue curve) is marginal at all temperatures. (3) Optical phonon limits the mobility at temperatures above 100 K. In particular, from 300 to 100 K a power law temperature dependence of  $\mu \sim T^{-\gamma}$  can be fitted with  $\gamma$  approaching 1.15 at  $V_{ds} = 2$  V as mentioned earlier. Comparing to the results from previously reported  $MoS_2$  devices,<sup>16</sup> where  $\gamma = 1.4$  for back-gated device and 0.55 for dual-gated (both top-gate and back-gate are used) device,  $\gamma$  = 1.15 from our WS<sub>2</sub> device indicates that optical phonon mode quenching may occur. It has been shown by earlier studies that top gate using high-k dielectrics<sup>2,17,46-48</sup> is the reason to cause the suppression of optical phonons and screening of charged impurities and to improve the device mobility on MoS<sub>2</sub>. However, in our WS<sub>2</sub> device, the

VOL. 8 • NO. 10 • 10396-10402 • 2014

JAI

mobility is surprisingly high (up to 234 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) without such top gate/-k dielectric structure. This may imply that simple structure like a few layer WS<sub>2</sub> crystals on SiO<sub>2</sub> surface can also have optical phonon suppressed by other reasons. The overall charge scattering behavior of our WS<sub>2</sub> device appears similarly to that of two-dimensional electron gas (2DEG) system containing low density and high mobility of electrons, such as AlGaN/GaN field-effect transistor.<sup>49</sup>

# CONCLUSIONS

In conclusion, we have successfully fabricated back gated field-effect transistors based on multilayer  $WS_2$  crystals with thermal SiO<sub>2</sub> as the dielectric layer and pure gold as the contact metal. These devices exhibit

on/off ratios up to 10<sup>8</sup> and mobilities reaching 234  $cm^2 V^{-1} s^{-1}$  at room temperature. We found that the device performance strongly depends on the thickness of WS<sub>2</sub> channel crystal and the best performance appears in the thickness between 6 and 10 nm. By studying low temperature transport behavior, we have identified that the high performance of our device is a combined result of low contact Schottky barrier and shallow impurity level inside WS<sub>2</sub> crystal. We also revealed that the scattering of charge carriers is mainly caused by optical phonons and charge impurities. Our work demonstrates that, comparing to other semiconducting TMDs, multilayer WS<sub>2</sub> crystal is indeed an excellent channel material for the making of high performance FET required for both energy saving and high power electronics applications.

# ARTICLE

### **METHODS**

The high quality  $WS_2$  bulk single crystals were synthesized using chemical vapor transport<sup>50</sup> with iodine acting as transport agent. The standard micromechanical exfoliation technique<sup>2</sup> was adopted to obtain  $WS_2$  thin flakes on the substrate of silicon with 300 nm thermal oxide. The flakes with desired thicknesses were screened by using an optical microscope *via* color contrast. Then 35 nm gold metal contacts connecting the  $WS_2$ flakes were patterned and deposited by using standard electron beam lithography and thermal evaporation. Then, the devices were annealed in forming gas at 200 °C for 2 h in order to remove organic residues introduced during the fabrication process. The accurate thickness of  $WS_2$  flakes was further determined using atomic force microscope (AFM).

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. We acknowledge Cleanroom Facility and Coordinated Instrumentation Facility at Tulane University for technical support of scanning electron microscopy and micro/ nanofabrication.

*Supporting Information Available:* Mobility histogram; Schottky barrier height extraction. This material is available free of charge *via* the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, *306*, 666–669.

- Novoselov, K. S.; Jiang, D.; Schedin, F.; Booth, T. J.; Khotkevich, V. V.; Morozov, S. V.; Geim, A. K. Two-Dimensional Atomic Crystals. *Proc. Natl. Acad. Sci. U.S.A.* 2005, 102, 10451–10453.

- Coleman, J. N.; Lotya, M.; O'Neill, A.; Bergin, S. D.; King, P. J.; Khan, U.; Young, K.; Gaucher, A.; De, S.; Smith, R. J.; *et al.* Two-Dimensional Nanosheets Produced by Liquid Exfoliation of Layered Materials. *Science* **2011**, *331*, 568–571.

- Lee, K.; Kim, H.-Y.; Lotya, M.; Coleman, J. N.; Kim, G.-T.; Duesberg, G. S. Electrical Characteristics of Molybdenum Disulfide Flakes Produced by Liquid Exfoliation. *Adv. Mater.* 2011, 23, 4178–4182.

- Smith, R. J.; King, P. J.; Lotya, M.; Wirtz, C.; Khan, U.; De, S.; O'Neill, A.; Duesberg, G. S.; Grunlan, J. C.; Moriarty, G.; *et al.* Large-Scale Exfoliation of Inorganic Layered Compounds in Aqueous Surfactant Solutions. *Adv. Mater.* **2011**, *23*, 3944.

- Wilson, J. A.; Yoffe, A. D. The Transition Metal Dichalcogenides Discussion and Interpretation of the Observed Optical, Electrical and Structural Properties. *Adv. Phys.* **1969**, *18*, 193–335.

- Mak, K. F.; Lee, C.; Hone, J.; Shan, J.; Heinz, T. F. Atomically Thin MoS<sub>2</sub>: A New Direct-Gap Semiconductor. *Phys. Rev. Lett.* 2010, *105*, 136805.

- Splendiani, A.; Sun, L.; Zhang, Y. B.; Li, T. S.; Kim, J.; Chim, C. Y.; Galli, G.; Wang, F. Emerging Photoluminescence in Monolayer MoS<sub>2</sub>. *Nano Lett.* **2010**, *10*, 1271–1275.

- Eda, G.; Yamaguchi, H.; Voiry, D.; Fujita, T.; Chen, M. W.; Chhowalla, M. Photoluminescence from Chemically Exfoliated MoS<sub>2</sub>. *Nano Lett.* **2011**, *11*, 5111–5116.

- Lebègue, S.; Eriksson, O. Electronic Structure of Two-Dimensional Crystals from *ab Initio* Theory. *Phys. Rev. B* 2009, 79, 115409.

- Kuc, A.; Zibouche, N.; Heine, T. Influence of Quantum Confinement on the Electronic Structure of the Transition Metal Sulfide TS<sub>2</sub>. *Phys. Rev. B* **2011**, *83*, 245213.

- Lopez-Sanchez, O.; Lembke, D.; Kayci, M.; Radenovic, A.; Kis, A. Ultrasensitive Photodetectors Based on Monolayer MoS<sub>2</sub>. *Nat. Nanotechnol.* **2013**, *8*, 497–501.

- Mak, K. F.; He, K. L.; Shan, J.; Heinz, T. F. Control of Valley Polarization in Monolayer MoS<sub>2</sub> by Optical Helicity. *Nat. Nanotechnol.* 2012, 7, 494–498.

- Zeng, H. L.; Dai, J. F.; Yao, W.; Xiao, D.; Cui, X. D. Valley Polarization in MoS<sub>2</sub> Monolayers by Optical Pumping. *Nat. Nanotechnol.* 2012, *7*, 490–493.

- Wu, S.; Ross, J. S.; Liu, G.-B.; Aivazian, G.; Jones, A.; Fei, Z.; Zhu, W.; Xiao, D.; Yao, W.; Cobden, D.; *et al.* Electrical Tuning of Valley Magnetic Moment Through Symmetry Control in Bilayer MoS<sub>2</sub>. *Nat. Phys.* **2013**, *9*, 149–153.

- Radisavljevic, B.; Kis, A. Mobility Engineering and a Metal-Insulator Transition in Monolayer MoS<sub>2</sub>. *Nat. Mater.* 2013, *12*, 815–820.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Li, H.-M.; Lee, D.-Y.; Choi, M. S.; Qu, D.; Liu, X.; Ra, C.-H.; Yoo, W. J. Metal-Semiconductor Barrier Modulation for High Photoresponse in Transition Metal Dichalcogenide Field Effect Transistors. *Sci. Rep.* **2014**, *4*, 404.

- Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- Liu, W.; Kang, J.; Sarkar, D.; Khatami, Y.; Jena, D.; Banerjee, K. Role of Metal Contacts in Designing High-Performance Monolayer n-Type WSe<sub>2</sub> Field Effect Transistors. *Nano Lett.* 2013, *13*, 1983–1990.

VOL. 8 • NO. 10 • 10396-10402 • 2014

- Larentis, S.; Fallahazad, B.; Tutuc, E. Field-Effect Transistors and Intrinsic Mobility in Ultra-Thin MoSe<sub>2</sub> Layers. *Appl. Phys. Lett.* **2012**, *101*, 223104.

- Chamlagain, B.; Li, Q.; Ghimire, N. J.; Chuang, H.-J.; Perera, M. M.; Tu, H.; Xu, Y.; Pan, M.; Xaio, D.; Yan, J.; *et al.* Mobility Improvement and Temperature Dependence in MoSe<sub>2</sub> Field-Effect Transistors on Parylene-C Substrate. *ACS Nano* **2014**, *8*, 5079.

- 23. Liu, L. T.; Kumar, S. B.; Ouyang, Y.; Guo, J. Performance Limits of Monolayer Transition Metal Dichalcogenide Transistors. *IEEE Trans. Electron Devices* **2011**, *58*, 3042–3047.

- Hwang, W. S.; Remskar, M.; Yan, R. S.; Protasenko, V.; Tahy, K.; Chae, S. D.; Zhao, P.; Konar, A.; Xing, H. L.; Seabaugh, A.; *et al.* Transistors with Chemically Synthesized Layered Semiconductor WS<sub>2</sub> Exhibiting 10<sup>5</sup> Room Temperature Modulation and Ambipolar Behavior. *Appl. Phys. Lett.* **2012**, *101*, 013107.

- Braga, D.; Lezama, I. G.; Berger, H.; Morpurgo, A. F. Quantitative Determination of the Band Gap of WS<sub>2</sub> with Ambipolar Ionic Liquid-Gated Transistors. *Nano Lett.* **2012**, *12*, 5218–5223.

- Li, S.-L.; Wakabayashi, K.; Xu, Y.; Nakaharai, S.; Komatsu, K.; Li, W.-W.; Lin, Y.-F.; Aparecido-Ferreira, A.; Tsukagoshi, K. Thickness-Dependent Interfacial Coulomb Scattering in Atomically Thin Field-Effect Transistors. *Nano Lett.* 2013, 13, 3546–3552.

- Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R. Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors. ACS Nano 2012, 6, 5635–5641.

- Li, T.; Du, G.; Zhang, B.; Zeng, Z. Scaling Behavior of Hysteresis in Multilayer MoS<sub>2</sub> Field Effect Transistors. *Appl. Phys. Lett.* **2014**, *105*, 093107.

- Qiu, H.; Pan, L.; Yao, Z.; Li, J.; Shi, Y.; Wang, X. Electrical Characterization of Back-Gated Bi-Layer MoS<sub>2</sub> Field-Effect Transistors and the Effect of Ambient on Their Performances. *Appl. Phys. Lett.* **2012**, *100*, 123104.

- Cho, A.-J.; Yang, S.; Park, K.; Namgung, S. D.; Kim, H.; Kwon, J.-Y. Multi-Layer MoS<sub>2</sub> FET with Small Hysteresis by Using Atomic Layer Deposition Al<sub>2</sub>O<sub>3</sub> as Gate Insulator. *ECS Solid State Lett.* 2014, *3*, Q67–Q69.

- Jariwala, D.; Sangwan, V. K.; Late, D. J.; Johns, J. E.; Dravid, V. P.; Marks, T. J.; Lauhon, L. J.; Hersam, M. C. Band-Like Transport in High Mobility Unencapsulated Single-Layer MoS<sub>2</sub> Transistors. *Appl. Phys. Lett.* **2013**, *102*, 173107.

- Das, S.; Chen, H. Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- Calvet, L. E. Electrical Transport in Schottky Barrier MOS-FETs. Ph.D. Thesis, Yale University, 2001.

- Appenzeller, J.; Radosavljević, M.; Knoch, J.; Avouris, P. Tunneling versus Thermionic Emission in One-Dimensional Semiconductors. *Phys. Rev. Lett.* 2004, *92*, 048301.

- Kam, K. K.; Parkinson, B. A. Detailed Photocurrent Spectroscopy of the Semiconducting Group VIB Transition Metal Dichalcogenides. J. Phys. Chem. 1982, 86, 463–467.

- 36. Le Comber, P. G.; Spear, W. E. Electronic Transport in Amorphous Silicon Films. *Phys. Rev. Lett.* **1970**, *25*, 509–511.

- 37. Sze, S. M. Semiconductor Devices: Pioneering Papers; World Scientific Publishing Company: Singapore, 1991.

- Kim, S.; Konar, A.; Hwang, W.-S.; Lee, J. H.; Lee, J.; Yang, J.; Jung, C.; Kim, H.; Yoo, J.-B.; Choi, J.-Y.; *et al.* High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer MoS<sub>2</sub> Crystals. *Nat. Commun.* **2012**, *3*, 1011.

- Gelmont, B. L.; Shur, M.; Stroscio, M. Polar Optical-Phonon Scattering in 3-Dimesional and 2-Dimensional Electron Gases. J. Appl. Phys. **1995**, 77, 657–660.

- Lisesivdin, S. B.; Acar, S.; Kasap, M.; Ozcelik, S.; Gokden, S.; Ozbay, E. Scattering Analysis of 2DEG Carrier Extracted by QMSA in Undoped Al<sub>0.25</sub>Ga<sub>0.75</sub>N/GaN Heterostructures. *Semicond. Sci. Technol.* **2007**, *22*, 543–548.

- 41. Hess, K. Impurity and Phonon-Scattering in Layered Structures. *Appl. Phys. Lett.* **1979**, *35*, 484–486.

- Lee, K.; Shur, M. S.; Drummond, T. J.; Morkoc, H. Low Field Mobility of 2-D Electron-Gas in Modulation Doped Alxga1-Xas/Gaas Layers. J. Appl. Phys. 1983, 54, 6432–6438.

- Molina-Sanchez, A.; Wirtz, L. Phonons in Single-Layer and Few-Layer MoS<sub>2</sub> and WS<sub>2</sub>. *Phys. Rev. B* **2011**, *84*, 155413.

Shi, H.: Pan, H.: Zhang, Y.-W.: Yakobson, B. I. Quasiparticle

- Shi, H.; Pan, H.; Zhang, Y.-W.; Yakobson, B. I. Quasiparticle Band Structures and Optical Properties of Strained Monolayer MoS<sub>2</sub> and WS<sub>2</sub>, *Phys. Rev. B* 2013, *87*, 155304.

- Burson, K. M.; Cullen, W. G.; Adam, S.; Dean, C. R.; Watanabe, K.; Taniguchi, T.; Kim, P.; Fuhrer, M. S. Direct Imaging of Charged Impurity Density in Common Graphene Substrates. *Nano Lett.* **2013**, *13*, 3576–3580.

- Kaasbjerg, K.; Thygesen, K. S.; Jacobsen, K. W. Phonon-Limited Mobility in n-type Single-Layer MoS<sub>2</sub> From First Principles. *Phys. Rev. B* **2012**, *85*, 115317.

- Wang, Q. H.; Kalantar-Zadeh, K.; Kis, A.; Coleman, J. N.; Strano, M. S. Electronics and Optoelectronics of Two-Dimensional Transition Metal Dichalcogenides. *Nat. Nanotechnol.* **2012**, *7*, 699–712.

- Ayari, A.; Cobas, E.; Ogundadegbe, O.; Fuhrer, M. S. Realization and Electrical Characterization of Ultrathin Crystals of Layered Transition-Metal Dichalcogenides. J. Appl. Phys. 2007, 101, 014507.

- Henriksen, E. A.; Syed, S.; Ahmadian, Y.; Manfra, M. J.; Baldwin, K. W.; Sergent, A. M.; Molnar, R. J.; Stormer, H. L. Acoustic Phonon Scattering in a Low Density, High Mobility AlGaN/GaN Field-Effect Transistor. *Appl. Phys. Lett.* 2005, *86*, 252108.

- Lieth, R. M. A. Preparation and Crystal Growth of Materials with Layered Structures; D. Reidel Publication Co.: Boston, MA, 1977.